Ultra-Compact, High-Performance FEC Core Cuts Costs

Xilinx Inc. unveiled an expanded Forward Error Correction (FEC) Intellectual Property (IP) Core offering at the WDM and Next Generation Optical Networking 2012 Conference this week in Monaco.

The offering includes GFEC, EFEC and high-gain FEC (xFEC) solutions used to obtain error control in signal transmission and to extend the distance of a transmission that reduces the number of regenerators (hops) along the route, which reduces both opex and capex for network operators, the company says.

Different FEC schemes provide different levels of coding gain. The higher the coding gain, the greater the distance an optical signal can be transmitted. As an example, the Xilinx 100G xFEC provides an industry leading 9.4dB NECG at 6.7 percent OH that increases 100G transmission distances and reduces 100G transmission power.

“The ultra-compact, high-performance FEC cores – which include GFEC IP cores for 2.5G, 10G, 40G, 100G applications, legacy 10G EFECs and a Xilinx xFEC IP core for 100G applications – were optimized specifically for Xilinx FPGAs to occupy less silicon real estate than non-Xilinx IP cores, making them the smallest FEC cores available,” the company adds. “Xilinx is also working to add 400G GFEC for leading-edge applications to be available 2Q13. Combined with partial reconfiguration, these IP cores optimized for Xilinx FPGAs enable customers to integrate multiple FEC standards on multiple interfaces while reducing product costs, power consumption and maximize network interoperability.”

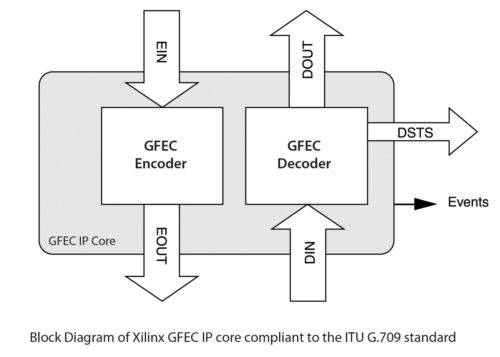

The Xilinx OTU1, 2, 3 and 4 (2.5G, 10G, 40G and 100G) GFEC IP cores are compliant with the ITU G.709 standard and are available today; the 100G high gain xFEC will be available in December. Xilinx says it will add other EFEC standard implementations based on customer demand.